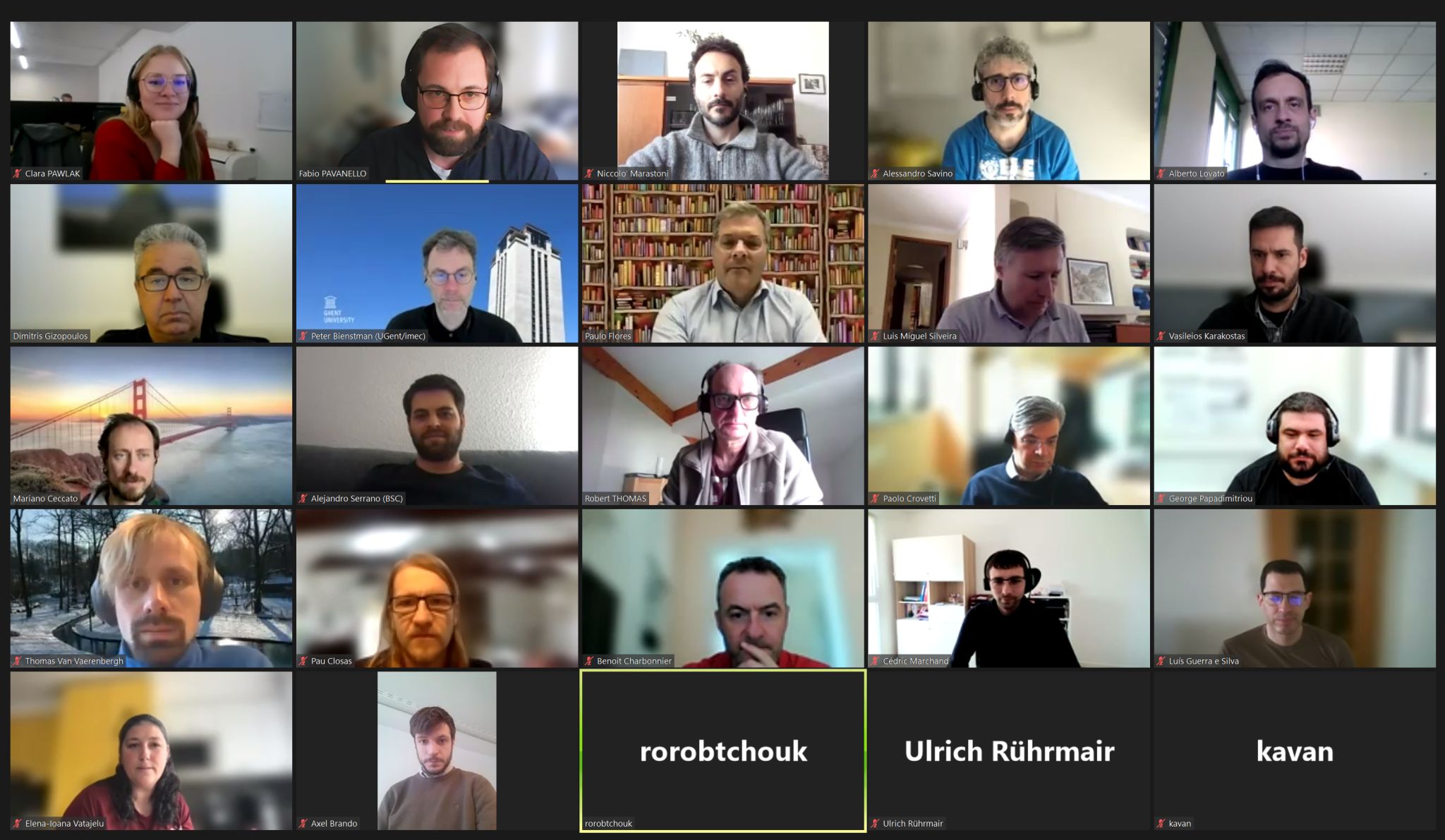

NEUROPULS First General Assembly in Lisbon

The inaugural session of the NEUROPULS Project General Assembly, hosted by Luis Miguel Silveira and team at the Institute of Systems and Computer Engineering, Research and Development, took place in Lisbon on September 4-5, 2023. The assembly brought together 27 members from prestigious institutions.View more

Watch our first video on NEUROPULS YouTube channel!

Explore the future of computing with our first video: The Neuropuls Project unveils secure, energy-efficient hardware accelerators powered by revolutionary neuromorphic technology, explained by the partners.View more

Abstract

The Future of Computing: Unlocking the Potential of Neuromorphic Technology for Low-Power and Secure Edge Computing. With the rise of self-driving vehicles, IoT, and Industry 4.0, the need for processing massive amounts of data locally and securely has never been greater. Traditional electronic computing systems have limitations such as high latency and low energy-efficiency, which are no longer suitable for these applications. Neuromorphic computing, a brain-inspired approach, is the solution to these problems.

However, current neuromorphic electrical computing systems have their own limitations, which is why the NEUROPULS project is developing next-generation low-power and secure edge-computing systems. By utilizing novel photonic computing architectures and security layers based on photonic PUFs, augmented silicon photonics CMOS-compatible platforms, and emerging non-volatile phase change materials, this project aims to demonstrate a two-order of magnitude improvement in energy efficiency. With RISC-V compliant interfaces and a novel full-system simulation platform, NEUROPULS will revolutionize the future of computing.

Objectives

NEUROPULS will develop -for the first time- secure hardware accelerators based on novel neuromorphic architectures and PUF-based security layers leveraging the benefits offered by the integration of photonics, PCMs and III-V materials. This integration will provide superior security, energy-efficiency, and speeds for spiking and formal recurrent NNs when compared to current available technology for the selected use-cases.

- Objective 1: Development of a CMOS-compatible platform addressing the integration of silicon photonics with PCMs and III-V materials

- Objective 2: Development of a low-power and secure RISC-V interfaced neuromorphic accelerator based on the integration of silicon photonics, novel PCMs, and Q-switched III-V lasers

- Objective 3: Development of a system-level simulation platform for PCM-based photonic low-power accelerators using photonic security layers

This project has received funding from the European Union’s Horizon Europe research and innovation programme under grant agreement No 101070238 . This publication [communication] reflects the views only of the author, and the Commission cannot be held responsible for any use which may be made of the information contained therein.

graph - chart

news

events

Project General Assembly #1

NEUROPULS has announced that its first project general assembly will be held on September 4 and 5 of this year in Lisbon, Portugal. The assembly will be hosted by INESC-ID, one of the project's partners to discuss the progress of the project and plan for future activities.

NEUROPULS Kick-Off Meeting - 2023

Ecully (FR)

documents

D1.2 Data Management Plan

D7.1 Visual identity, project website and social network account

NEUROPULS Project presentation A3 Poster

NEUROPULS Project presentation A5 Flyer

NEUROPULS Use cases A0 Scientific Poster

.svg.png)

.png)

.png)